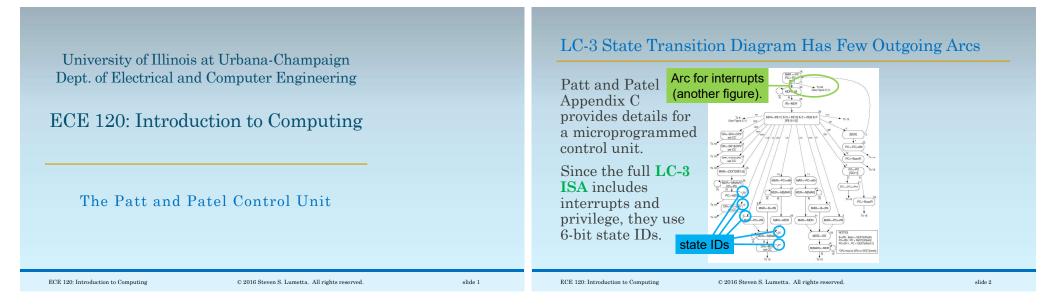

#### Microprogrammed Control Treats States as Instructions

Interrupts and privilege add 14 bits of control signals, bringing the total to 39.

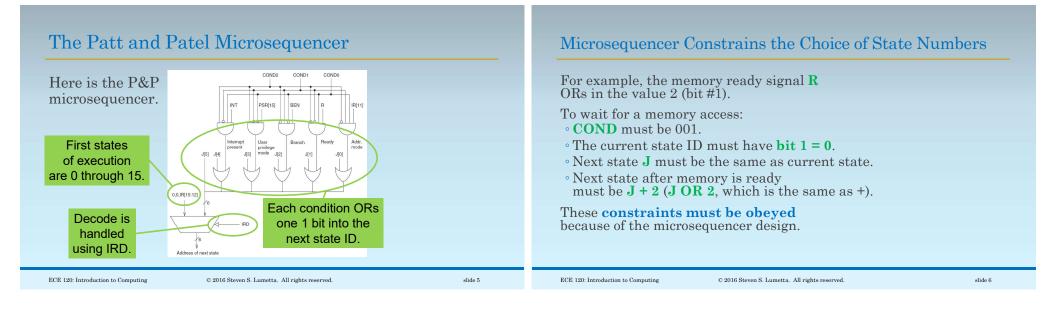

The P&P microinstructions also include 10 bits of sequencing information:

- J, a 6-bit next state ID

- COND, a 3-bit branch condition,

- and **IRD**, which indicates whether the current state is the decode state (#32).

#### **Microinstruction Branch Conditions for LC-3**

| COND | branch<br>on signal | meaning                  |

|------|---------------------|--------------------------|

| 000  | (none)              | unconditional            |

| 001  | R                   | memory ready             |

| 010  | BEN                 | <b>BR</b> taken          |

| 011  | IR[11]              | JSR or JSRR              |

| 100  | <b>PSR[15]</b>      | privilege mode violation |

| 101  | INT                 | interrupt occurred       |

Grey entries were not covered in our class.

slide 3

### Consider the BR Instruction as an Example

Let's look at an example.

The **BR** opcode is 0, so the **BR** execution state is also #0.

State #0 branches on **BEN**:

- when **BEN** is false, the branch is not taken, so the next state is fetch (#18), and

- when **BEN** is true, the next state must be #22 (18 OR 4), as the microsequencer ORs 4 with **J** when **COND** = 2 and **BEN** = 1.

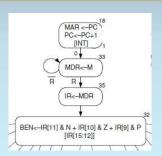

### How Does the LC-3 FSM Control Fetch and Decode?

Let's work out the microsequencing bits for instruction fetch and decode.

The figure to the right highlights these states.

slide 7

ECE 120: Introduction to Computing

| What are the Microsequencing Bits for Fetch 1?                        |                                                                                           |         |        |                                                            | What are the Microsequencing Bits for Fetch 2? |                      |      |               |                    |                |          |     |  |

|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------|---------|--------|------------------------------------------------------------|------------------------------------------------|----------------------|------|---------------|--------------------|----------------|----------|-----|--|

| Fetch 1 branches on <b>INT</b> (interrupt).                           |                                                                                           |         |        |                                                            | Fetch 2 branches on <b>R</b> (memory ready).   |                      |      |               |                    |                |          |     |  |

| The next states are fetch 2 (100001) and start of interrupt (110001). |                                                                                           |         |        | The next states are fetch 2 (100001) and fetch 3 (100011). |                                                |                      |      |               |                    |                |          |     |  |

|                                                                       | state #                                                                                   |         | J      | COND                                                       | IRD                                            |                      |      | state #       |                    | J              | COND     | IRD |  |

|                                                                       | 010010                                                                                    | fetch 1 | 100001 | 101                                                        | 0                                              |                      |      | 010010        | fetch 1            | 100001         | 101      | 0   |  |

|                                                                       | 100001                                                                                    | fetch 2 |        |                                                            |                                                |                      |      | 100001        | fetch 2            | 100001         | 001      | 0   |  |

|                                                                       | 100011                                                                                    | fetch 3 |        |                                                            |                                                |                      |      | 100011        | fetch 3            |                |          |     |  |

|                                                                       | 100000                                                                                    | decode  |        |                                                            |                                                |                      |      | 100000        | decode             |                |          |     |  |

| ECE 120:                                                              | ECE 120: Introduction to Computing © 2016 Steven S. Lumetta. All rights reserved. slide 9 |         |        |                                                            | ECE 120: I                                     | ntroduction to Compu | ting | © 2016 Steven | S. Lumetta. All ri | ghts reserved. | slide 10 |     |  |

# What are the Microsequencing Bits for Fetch 3?

Fetch 3 does not branch.

The next state is decode (100000).

| state # |         | J      | COND | IRD |

|---------|---------|--------|------|-----|

| 010010  | fetch 1 | 100001 | 101  | 0   |

| 100001  | fetch 2 | 100001 | 001  | 0   |

| 100011  | fetch 3 | 100000 | 000  | 0   |

| 100000  | decode  |        |      |     |

# What are the Microsequencing Bits for Decode?

Decode goes to a state from 000000 to 001111, depending on the opcode IR[15:12].

| state # |         | J      | COND | IRD |

|---------|---------|--------|------|-----|

| 010010  | fetch 1 | 100001 | 101  | 0   |

| 100001  | fetch 2 | 100001 | 001  | 0   |

| 100011  | fetch 3 | 100000 | 000  | 0   |

| 100000  | decode  | хххххх | xxx  | 1   |

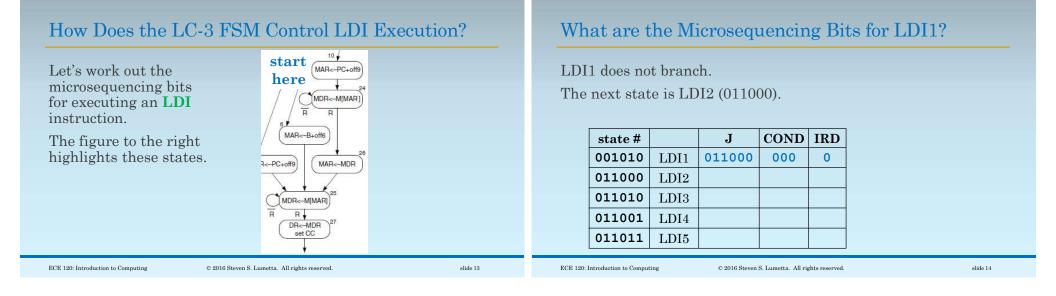

### What are the Microsequencing Bits for LDI2?

LDI2 branches on **R** (memory ready).

The next states are LDI2 (011000) and LDI3 (011010).

| state # |      | J      | COND | IRD |

|---------|------|--------|------|-----|

| 001010  | LDI1 | 011000 | 000  | 0   |

| 011000  | LDI2 | 011000 | 001  | 0   |

| 011010  | LDI3 |        |      |     |

| 011001  | LDI4 |        |      |     |

| 011011  | LDI5 |        |      |     |

## What are the Microsequencing Bits for LDI3?

LDI3 does not branch.

The next state is LDI4 (011001).

| state | #  |      | J      | COND | IRD |

|-------|----|------|--------|------|-----|

| 00101 | LO | LDI1 | 011000 | 000  | 0   |

| 01100 | 00 | LDI2 | 011000 | 001  | 0   |

| 01101 | LO | LDI3 | 011001 | 000  | 0   |

| 01100 | )1 | LDI4 |        |      |     |

| 01101 | L1 | LDI5 |        |      |     |

ECE 120: Introduction to Computing

© 2016 Steven S. Lumetta. All rights reserved.

slide 15

ECE 120: Introduction to Computing

© 2016 Steven S. Lumetta. All rights reserved.

## What are the Microsequencing Bits for LDI4?

LDI4 branches on **R** (memory ready).

The next states are LDI4 (011001) and LDI5 (011011).

| state # |      | J      | COND | IRD |

|---------|------|--------|------|-----|

| 001010  | LDI1 | 011000 | 000  | 0   |

| 011000  | LDI2 | 011000 | 001  | 0   |

| 011010  | LDI3 | 011001 | 000  | 0   |

| 011001  | LDI4 | 011001 | 001  | 0   |

| 011011  | LDI5 |        |      |     |

ECE 120: Introduction to Computing

© 2016 Steven S. Lumetta. All rights reserved.

slide 17

ECE 120: Introduction to Computing

LDI5 does not branch.

state # 001010

011000

011010

011001

011011

The next state is fetch 1 (010010).

LDI1

LDI2

LDI3

LDI4

LDI5

© 2016 Steven S. Lumetta. All rights reserved.

COND IRD

0

0

0

0

0

000

001

000

001

000

What are the Microsequencing Bits for LDI5?

J

011000

011000

011001

011001

010010

slide 18