## Find the Minimum Value Among Ten Integers

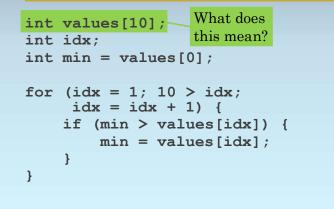

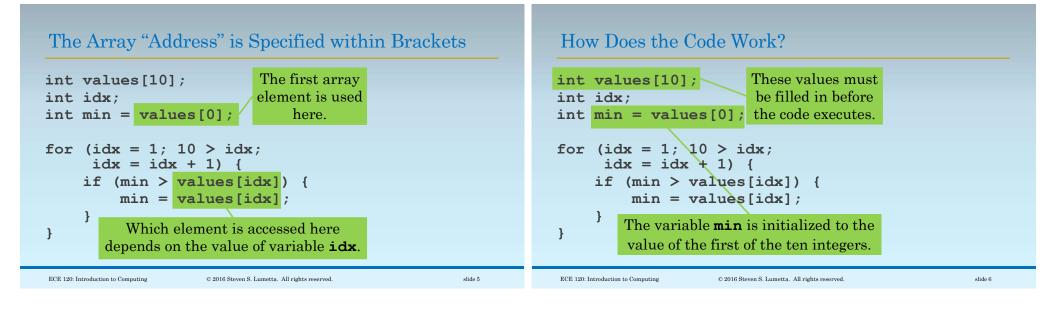

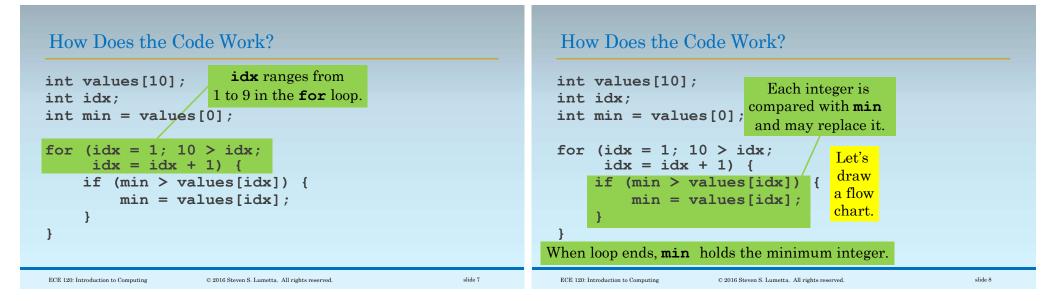

#### This Declaration Creates an Array of Ten Integers

| <pre>int values[10]; What does this mean?</pre>                                                                                                      |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| The variable declaration above creates<br>ten <b>32-bit 2's complement</b> numbers (ten <b>int</b> s).<br>• Such a group is called an <b>array</b> , |  |

| • and the declaration names<br>this particular group <b>"values</b> ".                                                                               |  |

| <ul> <li>Individual ints are then called<br/>values[0] through values[9].</li> </ul>                                                                 |  |

| An array is the <b>software analogue</b><br>of a memory.                                                                                             |  |

|                                                                                                                                                      |  |

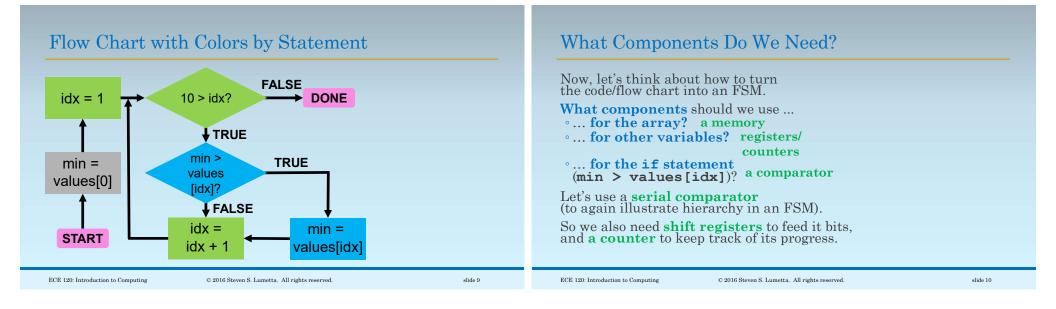

| FSM States Must Execute in a Fixed Number of Cycles                                                                                                                                                                                                                                                                                                                                         | Choice of Components Affects the FSM Design                                                                                                                                                                                                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| We have to <b>implement each high-level</b><br><b>FSM state in a fixed number of cycles</b><br>(or at least a controllable number of cycles).<br>Simple components imply more cycles<br>(slower, but smaller).<br>Complex components reduce the number of<br>states needed (larger, but may be faster).<br>For example, if we design a 10-operand<br>comparator, our task is fairly simple! | How we select components affects<br>• how we choose FSM states, and<br>• how the FSM moves between those states.<br>That's why we started by thinking<br>about components.<br>In a real design process, one goes back<br>and forth, tuning components to FSM,<br>and tuning FSM to components. |

| ECE 120: Introduction to Computing © 2016 Stoven S. Lumetta. All rights reserved. slide 11                                                                                                                                                                                                                                                                                                  | ECE 120: Introduction to Computing © 2016 Steven S. Lumetta. All rights reserved. slide 12                                                                                                                                                                                                     |

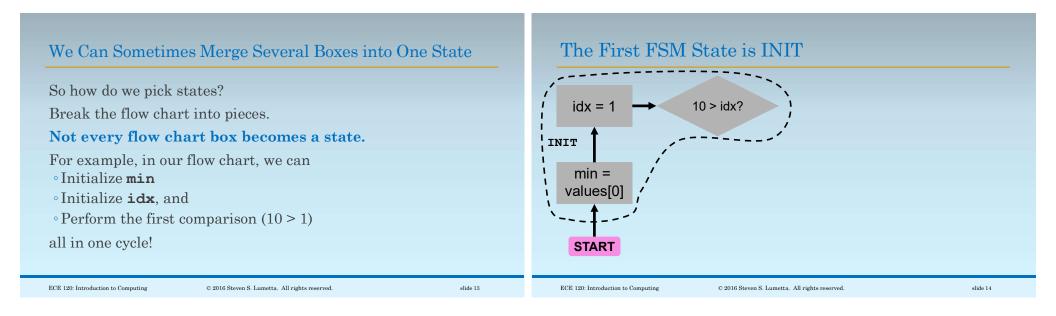

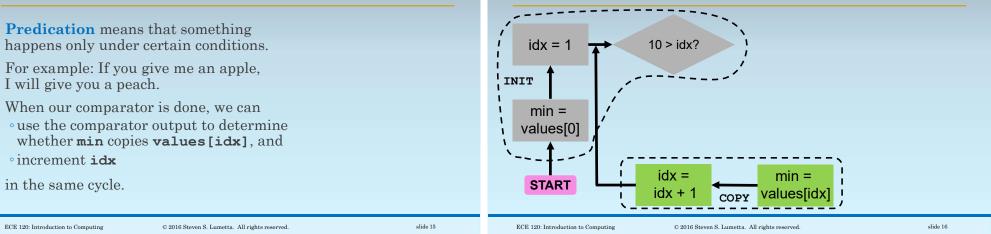

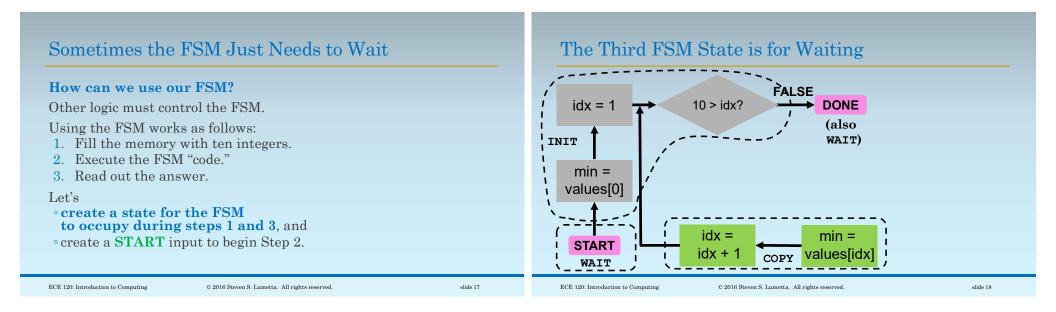

# We Can Predicate Execution with Logic

The Second FSM State May Copy a New Min Value

| Some Flow Chart Boxes May Require Multiple States                                                                                                           | Preparing for the Serial Comparison Requires a State                                                                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

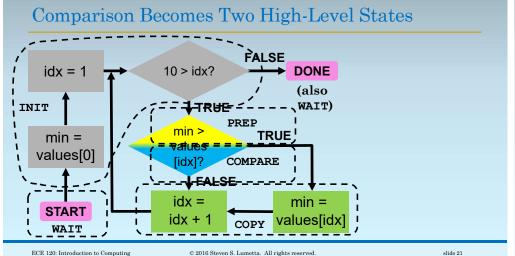

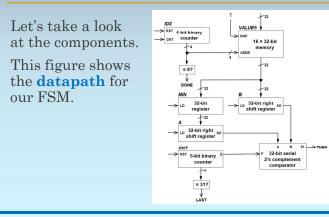

| What's left? Just the <b>if</b> statement.                                                                                                                  | In the <b>PREP</b> state, the FSM                                                                                                           |

| Sometimes                                                                                                                                                   | • Copies <b>min</b> to shift register <b>A</b> ,                                                                                            |

| • we may need more than one state                                                                                                                           | • Copies values[idx] to shift register <b>B</b> , and                                                                                       |

| • to implement a simple step in the flow chart.                                                                                                             | • Resets the <b>counter</b> to 0.                                                                                                           |

| Our <b>serial comparator</b><br>• takes bits from two <b>shift registers</b> , <b>A</b> and <b>B</b> ,<br>• and uses a <b>counter</b> to measure 32 cycles. | In the <b>COMPARE</b> state (for 32 cycles), the <b>serial comparator</b> performs the comparison.<br>When the <b>counter</b> has value 31, |

| We need to prepare <b>A</b> , <b>B</b> , and the <b>counter</b> for the comparison!                                                                         | the FSM moves to the <b>COPY</b> state.                                                                                                     |

| ECE 120: Introduction to Computing © 2016 Steven S. Lumetta. All rights reserved. slide 19                                                                  | ECE 120: Introduction to Computing © 2016 Steven S. Lumetta. All rights reserved. slide 20                                                  |

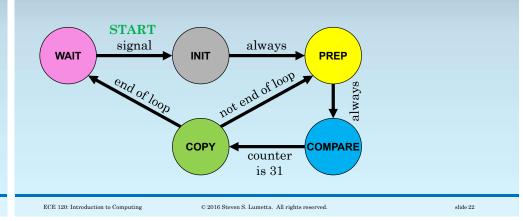

#### Redraw the Abstract State Transition Diagram

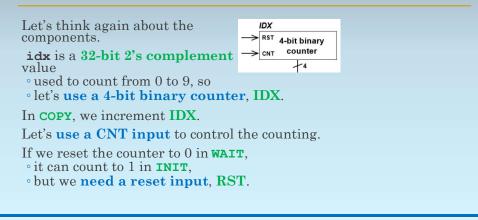

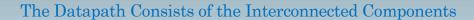

## IDX is a Binary Counter with CNT and RST Inputs

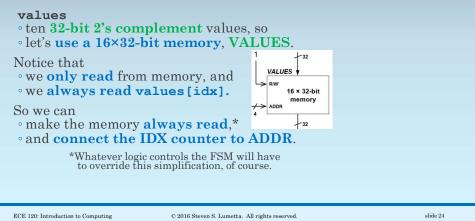

#### The Memory VALUES Can Use IDX as ADDR Input

ECE 120: Introduction to Computing

slide 23

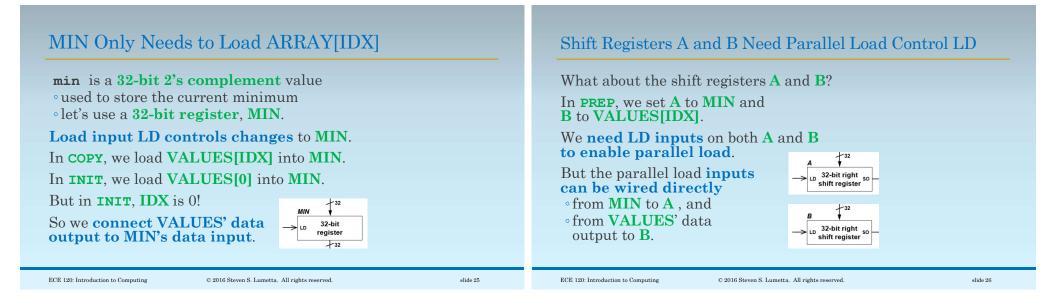

## Use a Binary Counter to Control the Comparator

Finally, we need a counter to drive the serial comparator for 32 cycles.

Let's use a 5-bit binary counter, CNT.

To reset the counter, use a reset input, RST.

Comparator has an **F** / "first bit" input.

CNT should generate a zero output Z.

ECE 120: Introduction to Computing

slide 27

ECE 120: Introduction to Computing

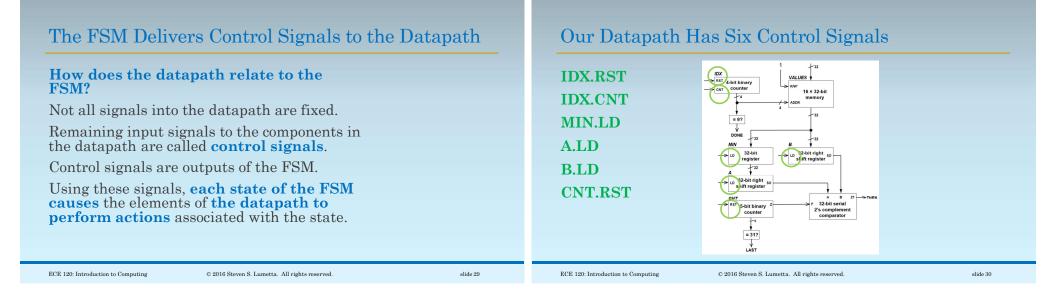

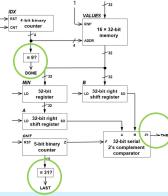

## FSM State Transitions Use Datapath Outputs

# The datapath also **produces output signals** that affect FSM state transitions.

Our datapath has three such signals:

- **DONE** the last loop iteration has finished

- LAST raised in the last cycle of serial comparison

- **THEN** a new minimum value has been found (A > B)

These signals are **inputs to the FSM**.

# Our Datapath Produces Three Outputs for the FSM

For our FSM, the datapath outputs are produced using simple logic. The **THEN** output depends on the representation used by the comparator; **Z1**

slide 31

means A > B.

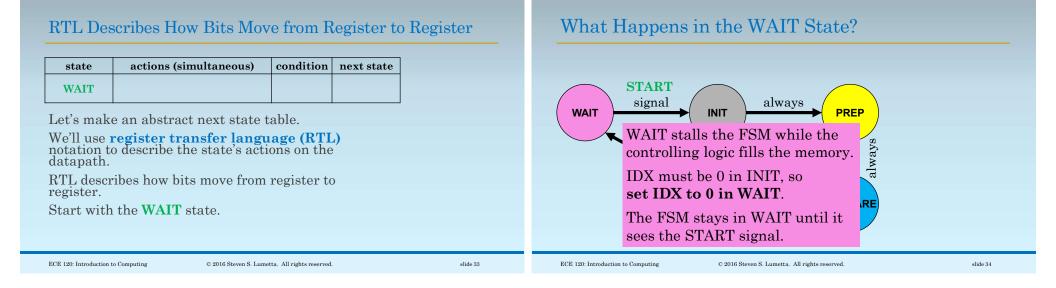

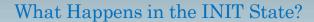

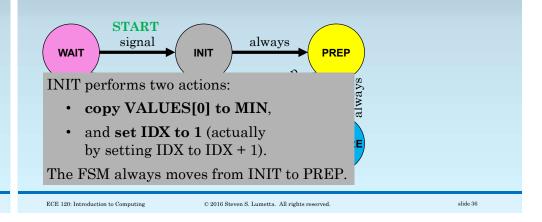

## Write the Information for WAIT

| state | actions (simultaneous) | condition | next state |

|-------|------------------------|-----------|------------|

|       | IDV 0                  | START     | INIT       |

| WAIT  | $IDX \leftarrow 0$     | START'    | WAIT       |

The **WAIT** state sets **IDX** to 0.

In RTL, we write "IDX  $\leftarrow 0$ " to indicate that the register IDX is filled with the value 0 (all 0 bits).

What about the next state(s)?

On START, move to INIT.

Otherwise, stay in WAIT.

ECE 120: Introduction to Computing

© 2016 Steven S. Lumetta. All rights reserved.

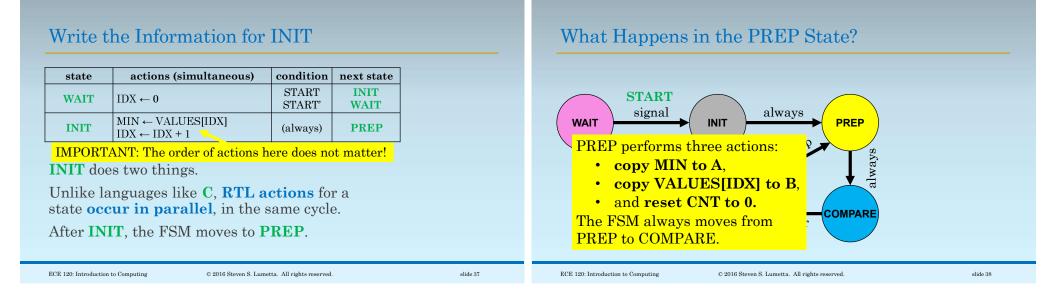

## Write the Information for PREP

| state | actions (simultaneous)                                                                                                                       | condition       | next state   |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------|

| WAIT  | $IDX \leftarrow 0$                                                                                                                           | START<br>START' | INIT<br>WAIT |

| INIT  | $\begin{array}{l} \text{MIN} \leftarrow \text{VALUES[IDX]} \\ \text{IDX} \leftarrow \text{IDX} + 1 \end{array}$                              | (always)        | PREP         |

| PREP  | $\begin{array}{l} \mathbf{A} \leftarrow \mathbf{MIN} \\ \mathbf{B} \leftarrow \mathbf{VALUES[IDX]} \\ \mathbf{CNT} \leftarrow 0 \end{array}$ | (always)        | COMPARE      |

Again, **RTL actions occur in parallel**, all in one cycle.

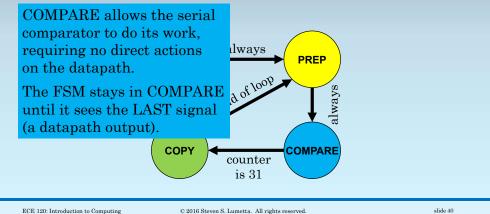

# What Happens in the COMPARE State?

ECE 120: Introduction to Computing

slide 39

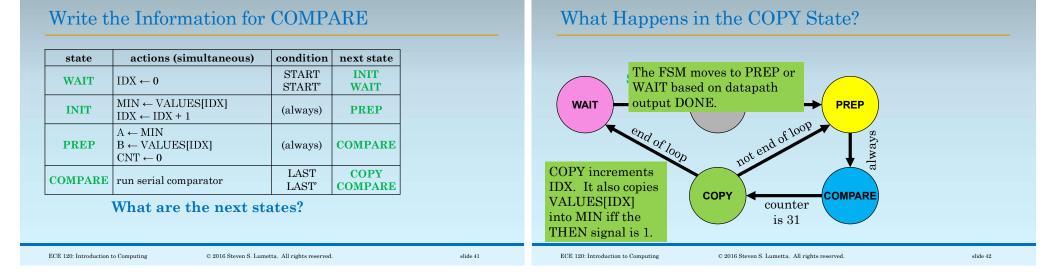

## Write the Information for COPY

| state   | actions (simultaneous)                                                                                                                       | condition       | next state      |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|

| WAIT    | $IDX \leftarrow 0$                                                                                                                           | START<br>START' | INIT<br>WAIT    |

| INIT    | $\begin{array}{l} \text{MIN} \leftarrow \text{VALUES[IDX]} \\ \text{IDX} \leftarrow \text{IDX} + 1 \end{array}$                              | (always)        | PREP            |

| PREP    | $\begin{array}{l} \mathbf{A} \leftarrow \mathbf{MIN} \\ \mathbf{B} \leftarrow \mathbf{VALUES[IDX]} \\ \mathbf{CNT} \leftarrow 0 \end{array}$ | (always)        | COMPARE         |

| COMPARE | run serial comparator                                                                                                                        | LAST<br>LAST    | COPY<br>COMPARE |

| СОРУ    | THEN: MIN $\leftarrow$ VALUES[IDX]<br>IDX $\leftarrow$ IDX + 1                                                                               | DONE<br>DONE'   | WAIT<br>PREP    |

#### Use a One-Hot Encoding to Represent States

| <b>WAIT</b> state: IDX $\leftarrow 0$ .<br>What are the control signals?                   |                                                                |             |             | <b>INIT</b> state:<br>MIN $\leftarrow$ VALUES[IDX], IDX $\leftarrow$ IDX + 1. |              |          |             |             |           |            |                                                                |             |             |            |          |          |             |  |

|--------------------------------------------------------------------------------------------|----------------------------------------------------------------|-------------|-------------|-------------------------------------------------------------------------------|--------------|----------|-------------|-------------|-----------|------------|----------------------------------------------------------------|-------------|-------------|------------|----------|----------|-------------|--|

| state                                                                                      | $\mathbf{S}_4\mathbf{S}_3\mathbf{S}_2\mathbf{S}_1\mathbf{S}_0$ | IDX.<br>RST | IDX.<br>CNT | MIN.<br>LD                                                                    |              | B.<br>LD | CNT.<br>RST |             |           | state      | $\mathbf{S}_4\mathbf{S}_3\mathbf{S}_2\mathbf{S}_1\mathbf{S}_0$ | IDX.<br>RST | IDX.<br>CNT | MIN.<br>LD | A.<br>LD | B.<br>LD | CNT.<br>RST |  |

| WAIT                                                                                       | 10000                                                          | 1           | 0           | 0                                                                             | 0            | 0        | 0           |             |           | WAIT       | 10000                                                          | 1           | 0           | 0          | 0        | 0        | 0           |  |

| INIT                                                                                       | 01000                                                          |             | Ju          | ist se                                                                        | t th         | e otł    | ner         |             |           | INIT       | 01000                                                          | 0           | 1           | 1          | 0        | 0        | 0           |  |

| PREP                                                                                       | 00100                                                          |             |             | gister                                                                        |              |          |             |             |           | PREP       | 00100                                                          |             |             |            |          |          |             |  |

| COMPAR                                                                                     | E 00010                                                        |             |             | ,<br>ead o                                                                    |              |          |             |             |           | COMPARE    | 00010                                                          |             |             |            |          |          |             |  |

| СОРУ                                                                                       | 00001                                                          |             | T           |                                                                               |              |          |             |             |           | СОРҮ       | 00001                                                          |             |             |            |          |          |             |  |

|                                                                                            |                                                                |             |             |                                                                               |              |          |             |             |           |            |                                                                |             |             |            |          |          |             |  |

| ECE 120: Introduction to Computing © 2016 Steven S. Lumetta. All rights reserved. slide 45 |                                                                |             |             | ECE 120: Introduction t                                                       | to Computing | c        | 2016 Steven | S. Lumetta. | All right | s reserved |                                                                | slide 46    |             |            |          |          |             |  |

# Fill in the Table of FSM Outputs Based on RTL

Fill in the Table of FSM Outputs Based on RTL

#### **PREP** state: A $\leftarrow$ MIN, B $\leftarrow$ VALUES[IDX], CNT $\leftarrow$ 0.

| state   | $\mathbf{S}_4\mathbf{S}_3\mathbf{S}_2\mathbf{S}_1\mathbf{S}_0$ | IDX.<br>RST | IDX.<br>CNT | MIN.<br>LD | A.<br>LD | B.<br>LD | CNT.<br>RST |

|---------|----------------------------------------------------------------|-------------|-------------|------------|----------|----------|-------------|

| WAIT    | 10000                                                          | 1           | 0           | 0          | 0        | 0        | 0           |

| INIT    | 01000                                                          | 0           | 1           | 1          | 0        | 0        | 0           |

| PREP    | 00100                                                          | 0           | 0           | 0          | 1        | 1        | 1           |

| COMPARE | 00010                                                          |             |             |            |          |          |             |

| СОРҮ    | 00001                                                          |             |             |            |          |          |             |

# Fill in the Table of FSM Outputs Based on RTL

Fill in the Table of FSM Outputs Based on RTL

#### **COMPARE** state: no RTL.

| state   | $\mathbf{S}_4\mathbf{S}_3\mathbf{S}_2\mathbf{S}_1\mathbf{S}_0$ | IDX.<br>RST | IDX.<br>CNT | MIN.<br>LD | A.<br>LD | B.<br>LD | CNT.<br>RST |

|---------|----------------------------------------------------------------|-------------|-------------|------------|----------|----------|-------------|

| WAIT    | 10000                                                          | 1           | 0           | 0          | 0        | 0        | 0           |

| INIT    | 01000                                                          | 0           | 1           | 1          | 0        | 0        | 0           |

| PREP    | 00100                                                          | 0           | 0           | 0          | 1        | 1        | 1           |

| COMPARE | 00010                                                          | 0           | 0           | 0          | 0        | 0        | 0           |

| СОРҮ    | 00001                                                          |             |             |            |          |          |             |

ECE 120: Introduction to Computing

slide 47

ECE 120: Introduction to Computing

## Fill in the Table of FSM Outputs Based on RTL

**COPY** state:  $IDX \leftarrow IDX + 1$ , THEN: MIN  $\leftarrow$  VALUES[IDX].

| state   | $\mathbf{S}_4\mathbf{S}_3\mathbf{S}_2\mathbf{S}_1\mathbf{S}_0$ | IDX.<br>RST | IDX.<br>CNT | MIN.<br>LD | A.<br>LD | B.<br>LD | CNT.<br>RST |

|---------|----------------------------------------------------------------|-------------|-------------|------------|----------|----------|-------------|

| WAIT    | 10000                                                          | 1           | 0           | 0          | 0        | 0        | 0           |

| INIT    | 01000                                                          | 0           | 1           | 1          | 0        | 0        | 0           |

| PREP    | 00100                                                          | 0           | 0           | 0          | 1        | 1        | 1           |

| COMPARE | 00010                                                          | 0           | 0           | 0          | 0        | 0        | 0           |

| СОРУ    | 00001                                                          | 0           | 1           | THEN       | 0        | 0        | 0           |

ECE 120: Introduction to Computing

© 2016 Steven S. Lumetta. All rights reserved.

slide 49

ECE 120: Introduction to Computing

© 2016 Steven S. Lumetta. All rights reserved.

slide 50

#### We Need Expressions for the Control Signals IDX.RST = $S_4$ IDX.CNT = $S_3 + S_0$ $MIN.LD = S_3 + THEN \cdot S_0$ (others) = $S_2$ IDX. IDX. MIN. A. В. CNT. $\mathbf{S}_4\mathbf{S}_3\mathbf{S}_2\mathbf{S}_1\mathbf{S}_0$ state RST CNT LD LD LD RST WAIT 10000 1 0 0 0 0 0 01000 1 0 0 INIT 0 1 0 00100 PREP 0 0 0 1 1 1 0 **COMPARE** 00010 0 0 0 0 0 COPY 00001 0 1 THEN 0 0 0 slide 51 ECE 120: Introduction to Computing © 2016 Steven S. Lumetta. All rights reserved.

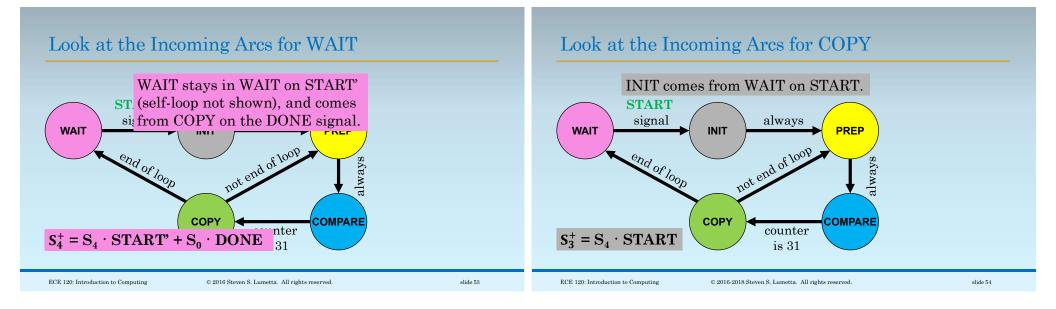

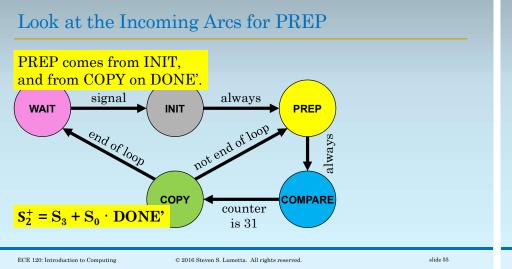

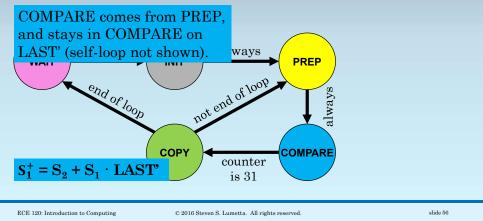

#### And Expressions for Next-State Logic

Expressions for next-state logic are similarly trivial.

However, must **look at incoming arcs** to write them.

## We Need Expressions for the Control Signals

| Quickly now |                                                                |             |             |            |          |          |             |  |  |  |  |

|-------------|----------------------------------------------------------------|-------------|-------------|------------|----------|----------|-------------|--|--|--|--|

| state       | $\mathbf{S}_4\mathbf{S}_3\mathbf{S}_2\mathbf{S}_1\mathbf{S}_0$ | IDX.<br>RST | IDX.<br>CNT | MIN.<br>LD | A.<br>LD | B.<br>LD | CNT.<br>RST |  |  |  |  |

| WAIT        | 10000                                                          | 1           | 0           | 0          | 0        | 0        | 0           |  |  |  |  |

| INIT        | 01000                                                          | 0           | 1           | 1          | 0        | 0        | 0           |  |  |  |  |

| PREP        | 00100                                                          | 0           | 0           | 0          | 1        | 1        | 1           |  |  |  |  |

| COMPARE     | 00010                                                          | 0           | 0           | 0          | 0        | 0        | 0           |  |  |  |  |

| СОРҮ        | 00001                                                          | 0           | 1           | THEN       | 0        | 0        | 0           |  |  |  |  |

Now we can see the value of our one-hot

state encoding. Express **IDX.RST**.

#### Look at the Incoming Arcs for COMPARE

#### If We Generalize the Instructions, We Have a Computer!

What if, instead, we design an FSM to execute some number of different statements.

We can use a **datapath** to manage bits.

We can use memory to give the FSM **instructions** as to what it should do (in terms of the FSM's built-in statements).

We can use sequences of **FSM states to** execute each instruction.

That's a computer!

slide 59