# **ECE 120 Second Midterm Exam** Spring 2016

Tuesday, March 15, 2016

| Name:              | UTIONS  | NetID:  |

|--------------------|---------|---------|

| Discussion Section | ):<br>  |         |

| 9:00 AM            | [ ] AB1 |         |

| 10:00 AM           | [ ] AB2 |         |

| 11:00 AM           | [ ] AB3 |         |

| 12:00 PM           | [ ] AB4 |         |

| 1:00 PM            | [ ] AB5 | [] ABA  |

| 2:00 PM            | [ ] AB6 |         |

| 3:00 PM            | [ ] AB7 | [ ] ABB |

| 4:00 PM            | [ ] AB8 | [ ] ABC |

| 5:00 PM            | [ ] AB9 | [ ] ABD |

|                    |         |         |

- Be sure that your exam booklet has 8 pages.

- Write your name, netid and check discussion section on the title page.

- Do not tear the exam booklet apart.

- Use backs of pages for scratch work if needed.

- This is a closed book exam. You may not use a calculator.

- You are allowed one handwritten 8.5 x 11" sheet of notes (both sides).

- Absolutely no interaction between students is allowed.

- Clearly indicate any assumptions that you make.

- The questions are not weighted equally. Budget your time accordingly.

Show your work.

| Total     | 100 points |  |

|-----------|------------|--|

|           |            |  |

| Problem 6 | 12 points  |  |

| Problem 5 | 17 points  |  |

| Problem 4 | 14 points  |  |

| Problem 3 | 18 points  |  |

| Problem 2 | 19 points  |  |

| Problem 1 | 20 points  |  |

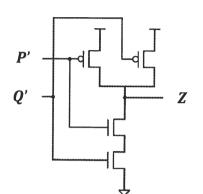

# Problem 1 (20 points): CMOS and Boolean properties

1. (5 points) Circle the correct choice for each statement. The inputs are inverted.

**a.** The output *Z* equals:

b. This example best illustrates the Boolean property:

**2.** (15 points) Let G(x,y,z) and H(x,y,z) be the 3-variable functions whose K-maps are given below.

- a. Express H(x,y,z) in canonical POS form

- i. Using the variables x, y, z:

$$H(x,y,z) = \frac{(x+y+z)(x'+y'+z)}{}$$

ii. Using the maxterm M<sub>i</sub> notation:

$$H(x,y,z) = M_0 M_0$$

**b.** Using your expression for *H* from part a.i), give the exact **dual of H**:

dual of

$$H(x,y,z) = \frac{YYZ + x'Y'Z}{}$$

c. Complete the K-map (below) for function F, so that  $F \oplus G = H$ . You must use don't cares wherever possible.

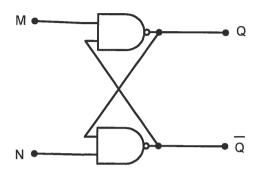

# Problem 2 (19 points): Sequential logic

1. (10 points) Consider the sequential feedback circuit shown below.

**a.** Complete the next-state table for this circuit

| М | N | Q⁺        |

|---|---|-----------|

| 0 | 0 | Forbidden |

| 0 | 1 | 1         |

| 1 | 0 | O         |

| 1 | 1 | Q         |

**b.** Express the next state  $Q^+$  as a function of M, N, and Q in **SOP form**.

$$Q^{\dagger} = \underline{M'N + MNQ} = \underline{M' + MNQ} = \underline{M'NQ'} + \underline{M'NQ + MNQ}$$

$$= \underline{M'N + NQ} = \underline{M' + NQ}$$

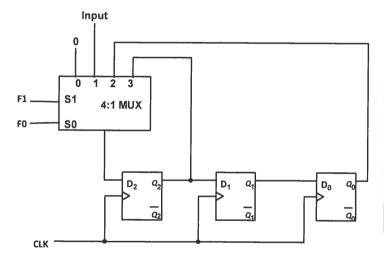

2. (9 points) Consider a 3-bit shift register that has the following diagram:

**a.** Determine the functionality of the register by completing the following table

| F <sub>1</sub> | Fo | Operation              |

|----------------|----|------------------------|

| 0              | 0  | Unused                 |

| 0              | 1  | Logical shift right    |

| 1              | 0  | Circular shift right   |

| 1              | 1  | Arithmetic shipt right |

**b.** If the shift register initially stores  $Q_2Q_1Q_0$ =100 and Input=0, what is stored in the register after one clock pulse and

$$F_1 F_0 = 01?$$

$$F_1$$

$F_0$  = 10? O (Assume again that 100 is stored before the operation.)

$$F_1$$

$F_0$  = 11? (Assume again that 100 is stored before the operation.)

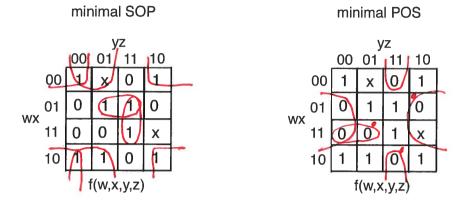

#### Problem 3 (18 points)

7

Consider the 4-variable function f(w,x,y,z), with the following K-map (drawn twice).

1. Give a minimal SOP expression for f(w,x,y,z) and show the corresponding loops on the left map.

map.

min SOP:

$$\overline{X}\overline{z} + \overline{X}\overline{y} + \overline{W}X\overline{z} + XY\overline{z}$$

$\overline{w}X\overline{z} + \overline{w}Xy$

2. Give a minimal POS expression for f(w,x,y,z) and show the corresponding loops on the right map.

min POS:

$$(\overline{x} + \overline{z})(\overline{w} + \overline{x} + y)(x + \overline{y} + \overline{z})$$

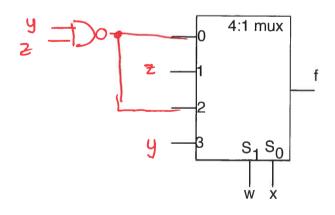

3. Implement f using only a 4:1 multiplexer (with select inputs  $S_1S_0 = wx$ ) and one NAND gate. Complemented inputs are not available.

#### Problem 4 (14 points)

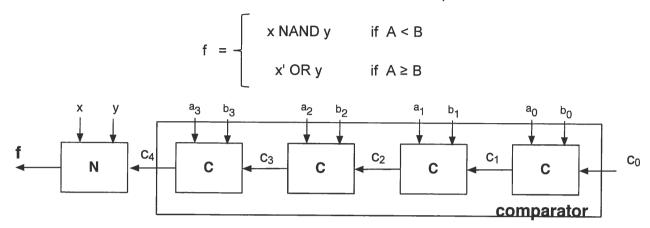

In this problem you will complete the design of the circuit shown below, which compares two 4-bit unsigned binary numbers  $A=a_3a_2a_1a_0$  and  $B=b_3b_2b_1b_0$  and outputs

1. (8 points) Design cell C so that the comparator portion of the above circuit operates correctly and outputs

$$c_4 = \begin{cases} 0 & \text{if } A < B \\ 1 & \text{if } A \ge B \end{cases}$$

a. Specify the input c<sub>0</sub>.

$\textbf{b.} \ \ \, \text{Express } c_{i+1} \text{ in terms of } c_i, \ a_i, \ b_i.$

2. (6 points) Design the network N by giving a Boolean expression for f.

$$f = C_y(\overline{xy}) + C_y(\overline{x}+y)$$

### Problem 5 (17 points)

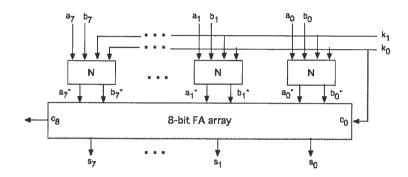

Shown below is an **8-bit arithmetic unit (AU)** which operates on two 8-bit **2's complement** numbers A and B. Each network N computes a\* and b\*, where:

$$a^* = k_1' k_0' + k_1 a$$

$b^* = k_1 k_0' b' + k_0 b + k_1' k_0' a$

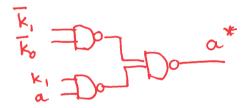

1. (4 points) Give a 2-level NAND gate implementation of a\*. Assume complemented inputs are available.

- 2. (13 points) Complete the table below.

- a. Give the values for a\*, b\*, c<sub>0</sub>

- b. Specify the operation performed. Express your answer as an **arithmetic function** (PLUS/MINUS) of A and B (e.g., "a plus the complement of b" is not an appropriate response).

| k <sub>1</sub> | k <sub>0</sub> | a* | b* | C <sub>0</sub> | Operation performed as a function of A and B (e.g. A PLUS/MINUS B) |  |  |  |

|----------------|----------------|----|----|----------------|--------------------------------------------------------------------|--|--|--|

| 0              | 0              | 1  | a  | O              | A MINUS 1                                                          |  |  |  |

| 0              | 1              | 0  | Ь  | 1              | B PLUS 1                                                           |  |  |  |

| 1              | 0              | α  | 6  | 0              | A MINUS B MINUS 1                                                  |  |  |  |

| 1              | 1              | a  | b  | 1              | A PLUS B PLUS 1                                                    |  |  |  |

### Problem 6 (12 points): Finite State Machines

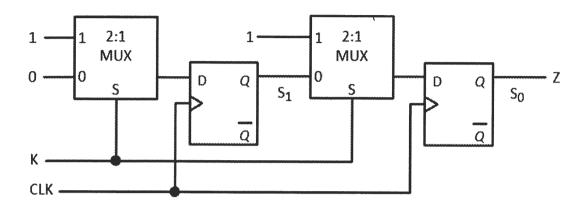

The circuit below is a 2-bit register that shifts right with serial input of 0 when K=0 and parallel loads with inputs of 1 when K=1.

1. (6 points) Complete the state transition table for the circuit.

| $S_1$ | $S_0$ | K | $S_1^+$ | $S_0^+$ | Z |

|-------|-------|---|---------|---------|---|

| 0     | 0     | 0 | O       | 0       | 0 |

| 0     | 0     | 1 | l       | l       | O |

| 0     | 1     | 0 | Ö       | 0       |   |

| 0     | 1     | 1 |         | 1       |   |

| 1     | 0     | 0 | 0       |         | O |

| 1     | 0     | 1 | ł       |         | O |

| 1     | 1     | 0 | 0       | 1       |   |

| 1     | 1     | 1 | l       |         |   |

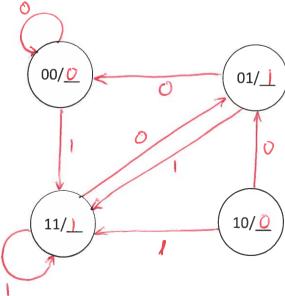

2. (6 points) Complete the state transition diagram for the circuit.

### Boolean algebra properties

Commutativity

$$x \cdot y = y \cdot x$$

$x + y = y + x$

Associativity  $(x \cdot y) \cdot z = x \cdot (y \cdot z)$   $(x + y) + z = x + (y + z)$

Distributivity  $x \cdot (y + z) = x \cdot y + x \cdot z$   $x + y \cdot z = (x + y) \cdot (x + z)$

Idempotence  $x \cdot x = x$   $x + x = x$

Identity  $x \cdot 1 = x$   $x + 0 = x$

Null  $x \cdot 0 = 0$   $x + 1 = 1$

Complementarity  $x \cdot x' = 0$   $x + x' = 1$

Involution  $(x')' = x$

DeMorgan's  $(x \cdot y)' = x' + y'$   $(x + y)' = x' \cdot y'$

Absorption  $x \cdot (x + y) = x$   $x + x \cdot y = x$

No-Name  $x \cdot (x' + y) = x \cdot y$   $x + x' \cdot y = x + y$

Consensus  $(x + y) \cdot (y + z) \cdot (x' + z) = x \cdot y + y \cdot z + x' \cdot z = x \cdot y + x' \cdot z$

Feel free to tear this page off and use it as scratch paper.